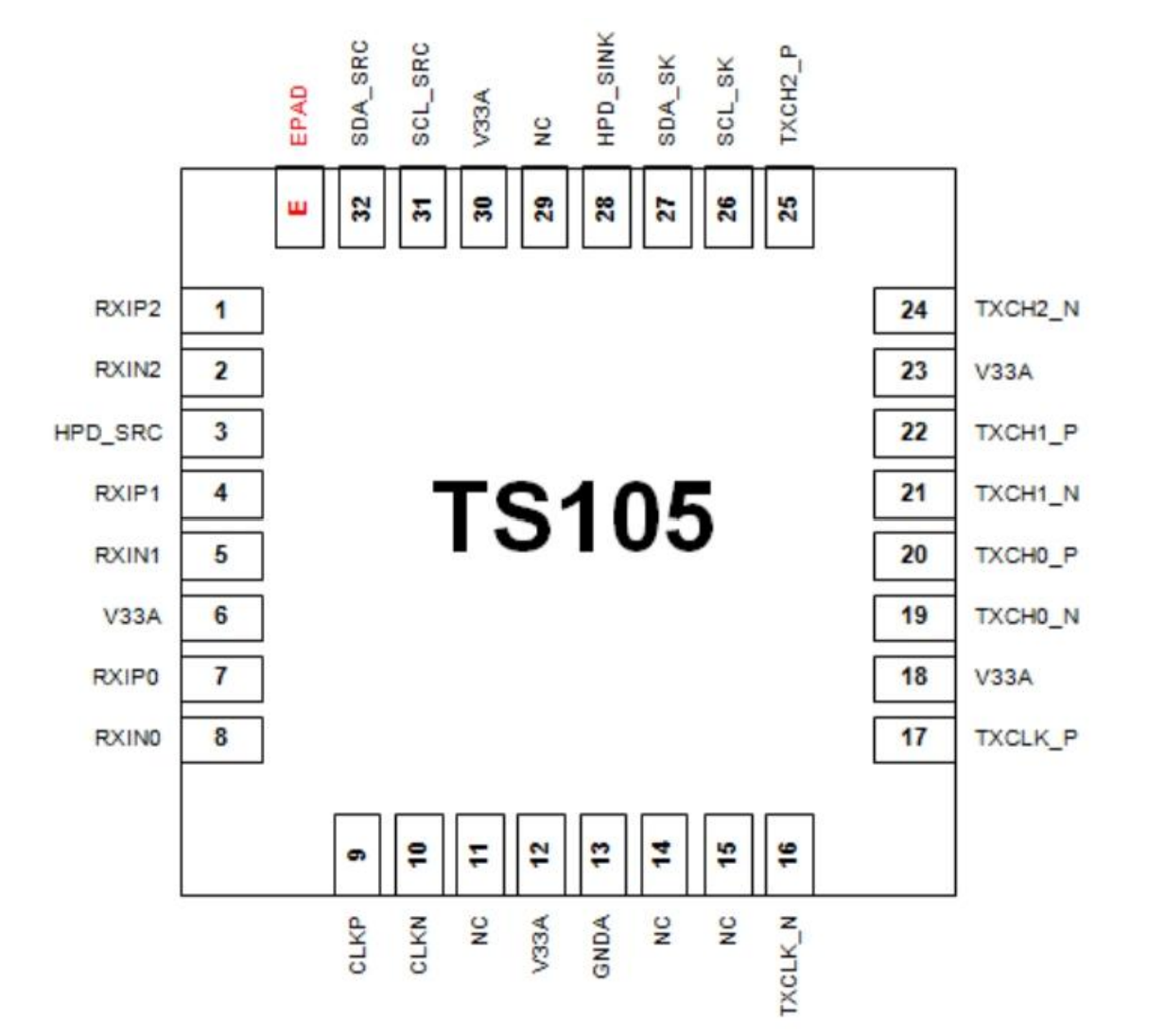

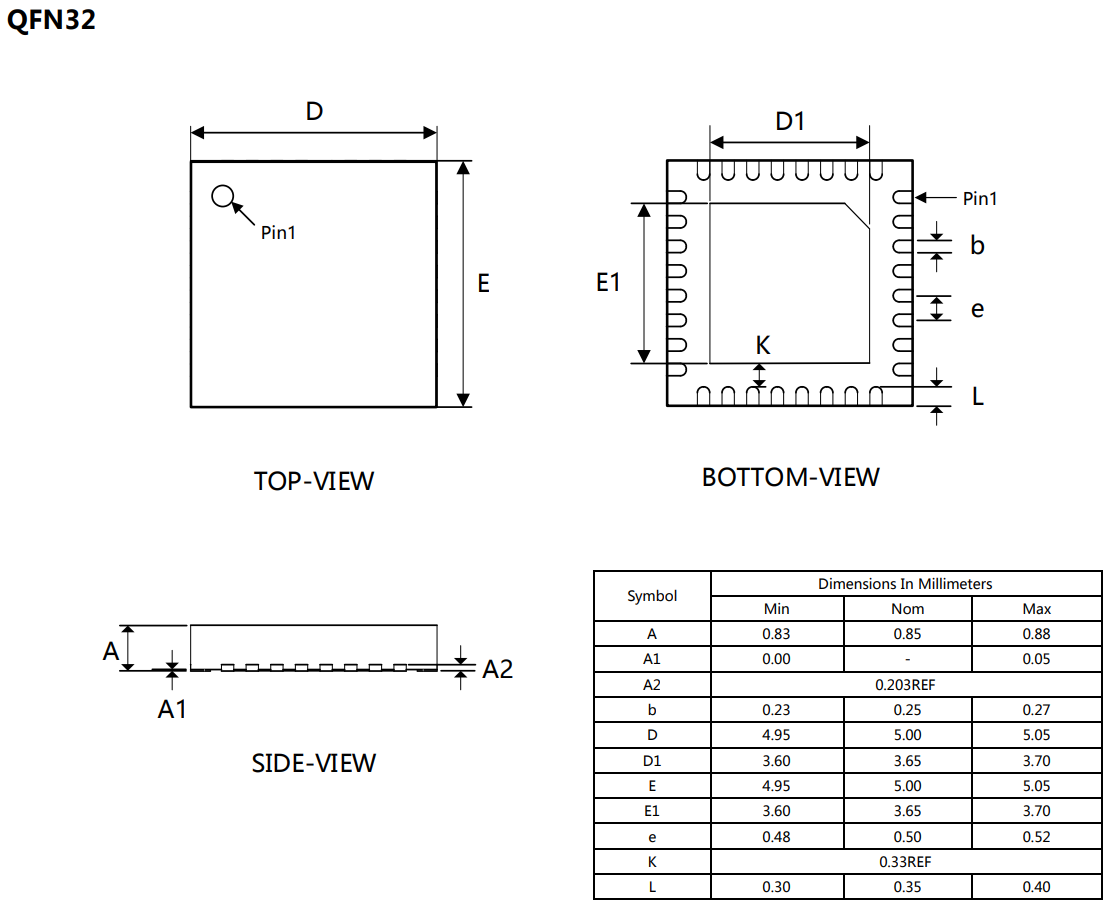

封裝

QFN32 (5*5*0.85).

DisplayPort信號中繼

每條通道高達3.4Gbps的HDMI/DVI電平轉換操作

支持HDMI 2.0 4:2:0 格式

集成50Ω終端電阻,用於交流耦合差動輸入

DDC/HPD電平轉換

支持DDC緩衝區

靜電防護最高可達6kV

QFN32 (5*5*0.85).

| 引腳 | 名稱 | 類型 | 描述 |

|---|---|---|---|

| 1 | RXIP2 | Input | 來自顯示源端的 TMDS 差分輸入的正信號. |

| 2 | RXIN2 | Input | 來自顯示源端的 TMDS 差分輸入的負信號. |

| 3 | HPD_SRC | Output | 3.3V HPD 檢測. |

| 4 | RXIP1 | Input | 來自顯示源端的 TMDS 差分輸入的正信號. |

| 5 | RXIN1 | Input | 來自顯示源端的 TMDS 差分輸入的負信號. |

| 6 | V33A | Power | 3.3V±10%直流電源. |

| 7 | RXIP0 | Input | 來自顯示源端的 TMDS 差分輸入的正信號. |

| 8 | RXIN0 | Input | 來自顯示源端的 TMDS 差分輸入的負信號. |

| 9 | CLKP | Input | 來自顯示源端的 TMDS 差分輸入的正時鐘信號. |

| 10 | CLKN | Input | 來自顯示源端的 TMDS 差分輸入的負時鐘信號. |

| 11 | NC | - | 保留. |

| 12 | V33A | Power | 3.3V±10%直流電源. |

| 13 | GNDA | GND | 接地. |

| 14 | NC | - | 保留. |

| 15 | NC | - | 保留. |

| 16 | TXCLK_N | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的負信號. |

| 17 | TXCLK_P | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的正信號. |

| 18 | V33A | Power | 3.3V±10%直流電源. |

| 19 | TXCH0_N | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的負信號. |

| 20 | TXCH0_P | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的正信號. |

| 21 | TXCH1_N | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的負信號. |

| 22 | TXCH1_P | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的正信號. |

| 23 | V33A | Power | 3.3V±10%直流電源. |

| 24 | TXCH2_N | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的負信號. |

| 25 | TXCH2_P | Output | HDMI 相容 TMDS 差分輸出到顯示接收器的正信號. |

| 26 | SCL_SK | I/O | 5V DDC 時鐘 I/O 連接到接收器設備. |

| 27 | SDA_SK | I/O | 5V DDC 資料 I/O 連接到接收器設備. |

| 28 | HPD_SINK | Input | 5V DDC 資料 I/O 連接到接收器設備.此信號來自 HDMI/DVI 接收器.如果 HPD_SINK=1,則表示“已插入”狀態;如果 HPD_SINK=0,則表示已拔出.HPD_SINK 內置下拉電阻. |

| 29 | NC | - | 保留. |

| 30 | V33A | Power | 3.3V±10%直流電源. |

| 31 | SCL_SRC | I/O | 3.3V DDC 時鐘 I/O 連接到接收器設備. |

| 32 | SDA_SRC | I/O | 3.3V DDC 資料 I/O 連接到接收器設備. |

| E | EPAD | - | 必須連接到地. |

電源電壓 3.3V±10%.

通過禁用輸入端(使用輸出使能)以及輸出端檢測(使用熱插拔檢測)實現省電模式.

| 參數 | 符號 | 最小值 | 典型值 | 最大值 | 單位 |

|---|---|---|---|---|---|

| 推薦的操作條件 | |||||

| 3.3V 電源 | VDD | 3.0 | 3.3 | 3.6 | V |

| 3.3V 電源電流 | IDD | - | - | 100 | mA |

| 工作溫度範圍 | T | - | - | 85 | ℃ |

| IDD@工作(165 MHz) | IOP | - | - | 100 | mA |

| In[4:1]+/-的電氣特性 | |||||

| 單位間隔 | TBIT | 360 | - | - | ps |

| 差動輸入峰-峰值電壓 | V RX-Diffp-p | - | - | 1.2 | V |

| INX 輸入對的最小眼寬 | TRX-EYE | 0.8 | - | - | Tbit |

| 交流峰值共模輸入電壓 | VCM-AC-pp | - | - | 100 | mV |

| 直流輸入阻抗 | ZRX-DC | 40 | 50 | 60 | Ω |

| RX 輸入端電壓 | VRX-Bias | 0 | - | 2 | V |

| 輸入處於高 Z 狀態時 INx 的單端輸入電阻 | ZRX-HIGH-Z | 100 | - | - | kΩ |

| OUT[4:1]+/-的電氣特性 | |||||

| 單端高電平輸出電壓 | VH | AVCC - 10mV | AVCC | AVCC + 10mV | V |

| 單端低電平輸出電壓 | VL | AVCC - 600mV | AVCC - 500mV | AVCC - 400mV | V |

| 單端輸出擺幅電壓 | VSWING | 400 | 500 | 600 | mV |

| 高 Z 狀態下的單端電流 | IOFF | - | - | 10 | uA |

| 上升時間 | TR | 125 | - | 0.4TBIT | ps |

| 下降時間 | TF | 125 | - | 0.4TBIT | ps |

| 對內差分偏斜 | TSKEW_INTRA | - | - | 10 | ps |

| 通道間對通道輸出偏差 | T SKEW_INTER | - | - | 250 | ps |

| 添加到 TMDS 信號的抖動 | T JIT | - | - | 25 | ps |

| PD#和 DDC_en 的電氣特性 | |||||

| 輸入高電平 | V IH | 2 | - | VDD | V |

| 輸入低電平 | VIL | 0 | - | 0.8 | V |

| 輸入漏電流 | IIN | - | - | 10 | uA |

| HPD_SINK 和 HPD_SRC 的電氣特性 | |||||

| HPD_SINK 輸入高電平 | VIH_HPD_SINK | 2 | 5 | 5.5 | V |

| HPD_SINK 輸入低電平 | VIL_HPD_SINK | 0 | - | 0.8 | V |

| HPD_SINK 輸入漏電流 | IIN_HPD_SINK | - | - | 50 | uA |

| HPD_SRC 輸出高電平 | VOH_HPD_SRC | 3 | - | 3.6 | V |

| HPD_SRC 輸出低電平 | VOL_HPD_SRC | 0 | - | 0.2 | V |

| HPD_SINK 到 HPD_SRC 傳播延遲 | THPD | - | - | 200 | ps |

| HPD_SRC 上升時間/下降時間 | TTRF-HPD_SRCC | 1 | - | 20 | ns |

| HPD_SINK 輸入下拉電阻 | RHPD | 100 | 200 | 300 | kΩ |

| SDA、SCL、SDA_SING 和 SCL_SING 的電氣特性 | |||||

| 輸入電壓 | VI-DDC | 0 | - | 5.5 | V |

| 輸入漏電 | VLK-DDC | - | - | 10 | uA |

| 輸入/輸出電容 | CI | - | - | 10 | pF |

| 開關電阻 | RON | - | - | 50 | Ω |

| Parameter | Range |

|---|---|

| 電源電壓 | -0.5V to 3.6V |

| 直流 輸入電壓 | -0.5V to 3.6V |

| 輸出電壓 | -0.5V to 3.6V |

| 儲存溫度 | -55℃ to 150℃ |

| 工作溫度 | 0℃ to 85℃ |

| ESD HBM | ± 6KV |

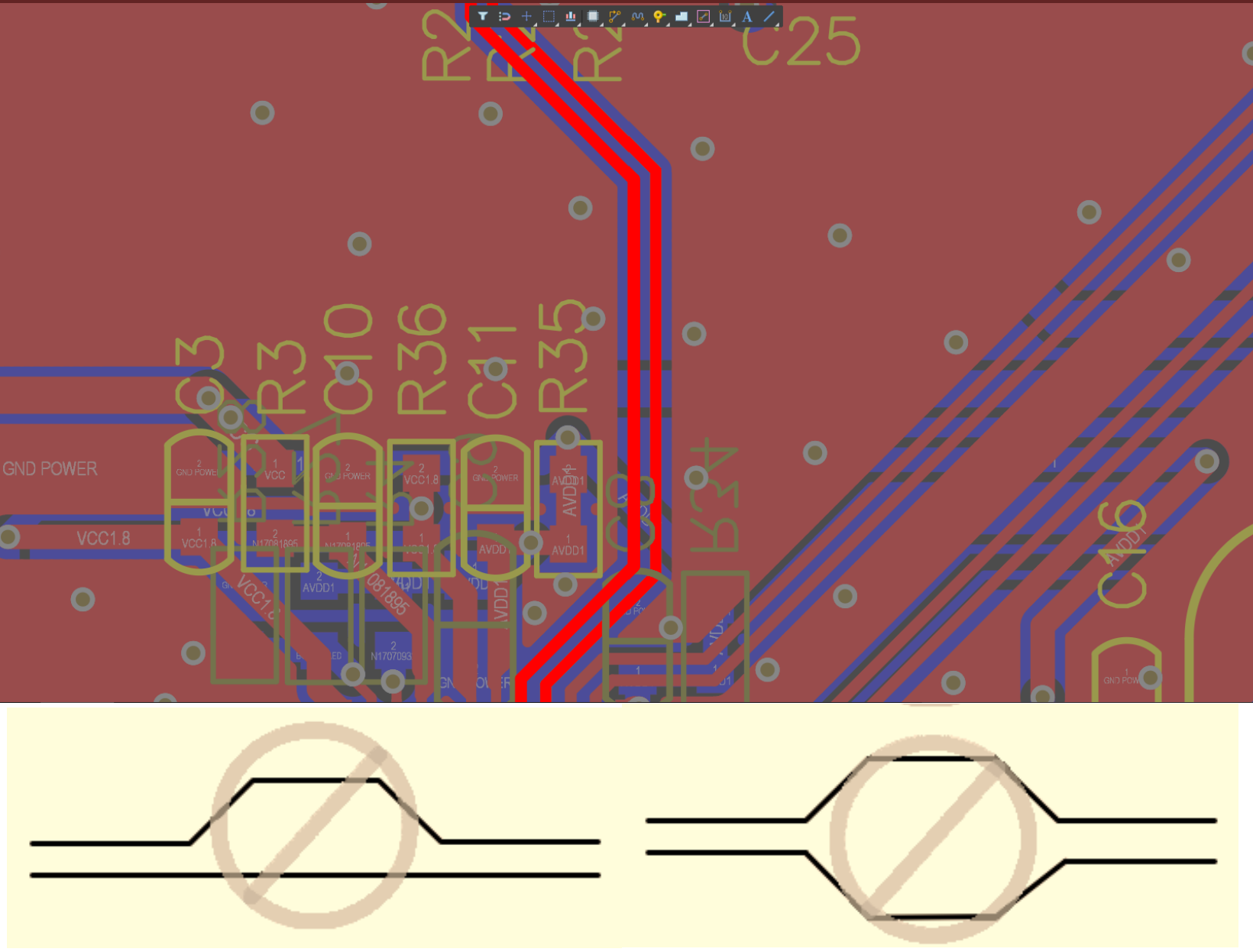

內線對的長度應該相等,並且走線對應該緊密佈線.差動通道上的部件或通孔必須對稱放置.差動對的兩條跡線之間的距離必須從頭到尾保持恒定.對於差分信號和跡線,差分阻抗的計算是必要的

HDMI 差動跡線阻抗:100 ohm+/-15%

顯示埠差動軌跡阻抗:100 ohm +/-15%

USB2.0 差動跟蹤阻抗:90 ohm +/-15%

USBC 型差動軌跡阻抗:90 ohm +/-15%

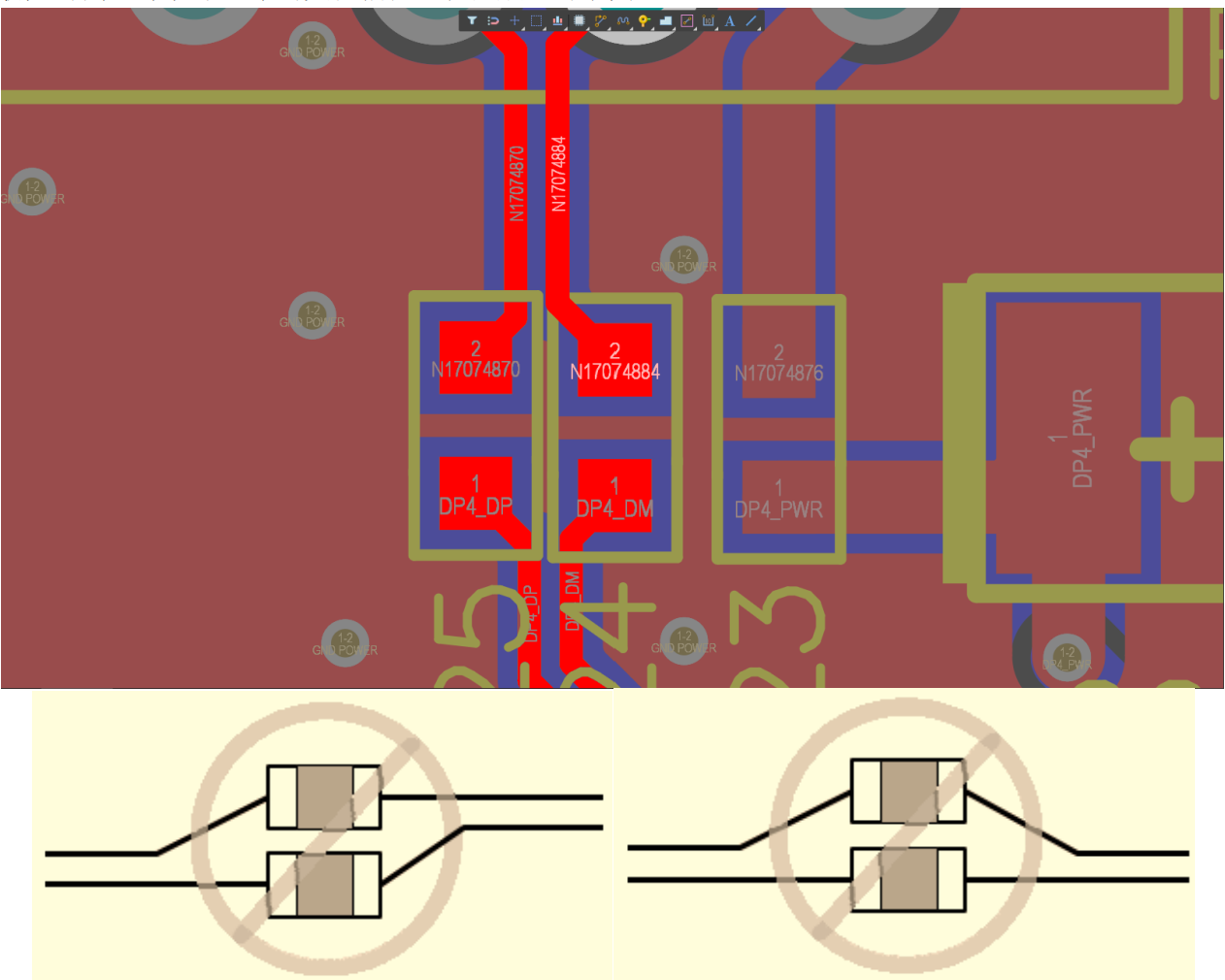

將所有高速差動對對稱且相互平行地佈線在一起.在佈線到連接器引腳時,自然會出現偏離此要求的情況,這些偏差必須同樣短

避免器件在高速信號跡線上包括表面貼裝器件(SMD),因為這些器件會引入可能對信號品質產生負面影響的不連續性.當信號線上需要 SMD 時(例如,USB 超高速傳輸交流耦合電容器),允許的最大組件尺寸為0603.強烈建議使用 0402 或更小的尺寸.在佈局過程中對稱放置這些元件,以確保最佳信號品質並將反射降至最低.瞭解正確和不正確的交流耦合電容器放置的示例

外露襯底焊盤(EPad)接地是封裝體的最佳散熱方式.為了滿足封裝功耗要求,需要將 ePad 焊接到 PCB 的接地上. 電路板上襯底焊盤邊緣和引線焊盤內側邊緣之間的間隙應設計為至少 0.25 mm,以避免短路.

| 文件 | 下載 |

|---|---|

| TS105簡體中文 | |

| TS105繁體中文 | |

| TS105英文 |